UVM Verification

|

UVM based Verification

RISC-V Verification

|

|

Design Verification Solutions

Yongatek Verification Team provides several IC design verification solutions through using an extensive range of industry gold standard tools and Verification IPs (VIP).

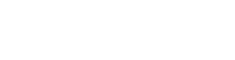

Functional Verification

Yongatek’s Functional Verification platform consists of tools that enhance productivity for design entry and HDL simulation. We apply Metric Driven Verification (MDV), using the Universal Verification Methodology (UVM).

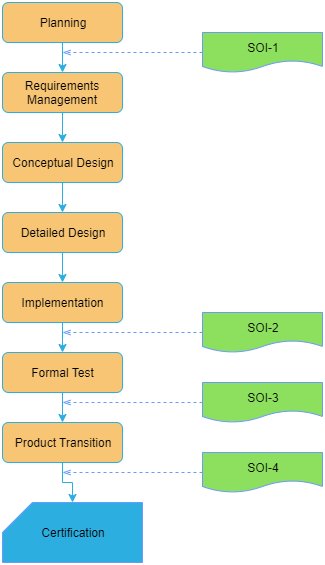

Requirements Management

With the designs getting more complex each day, the requirements grow significantly. Besides, the growing design complexity increases the necessity of well-documented problems and design definitions. This necessity gets even more highlighted with security-critical systems like DO-254 compliant designs. We provide design requirement documentation and traceability matrixes for designs to ensure that the product is built as intended.